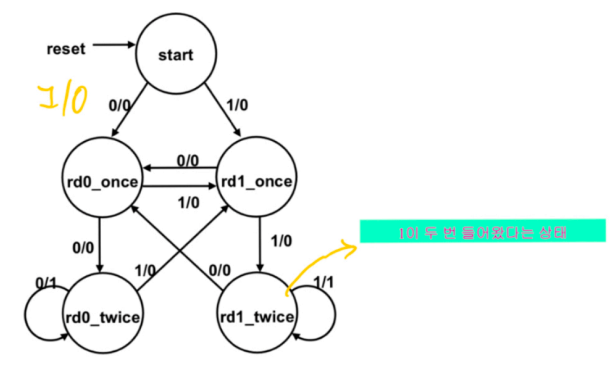

📄 상태 천이도

📄 회로 코드

module seq_det_mealy(clk, rst, din_bit, dout_bit, state_reg, next_state);

input clk, rst, din_bit; // din_bit : 입력값

output dout_bit; // 출력값. : 1이나 0이 연속으로 들어오면 1을, 아닌 경우 0을 출력한다.

output reg [2:0] state_reg, next_state;

// 상태 선언

parameter start = 3'b000;

parameter rd0_once = 3'b001;

parameter rd1_once = 3'b010;

parameter rd0_twice = 3'b011;

parameter rd1_twice = 3'b100;

// Next State Logic

always @(state_reg or din_bit) begin

case(state_reg)

start : if (din_bit==0) next_state <= rd0_once;

else if (din_bit==1) next_state <= rd1_once;

else next_state <= start;

rd0_once : if (din_bit==0) next_state <= rd0_twice;

else if (din_bit==1) next_state <= rd1_once;

else next_state <= start;

rd1_once : if (din_bit==0) next_state <= rd0_once;

else if (din_bit==1) next_state <= rd1_twice;

else next_state <= start;

rd0_twice : if (din_bit==0) next_state <= rd0_twice;

else if (din_bit==1) next_state <= rd1_once;

else next_state <= start;

rd1_twice : if (din_bit==0) next_state <= rd0_once;

else if (din_bit==1) next_state <= rd1_twice;

else next_state <= start;

default : next_state <= start;

endcase

end

//State Register : 클락이 들어올 때 다음 상태값을 넘겨주는 것.

always @(posedge clk or posedge rst) begin

if(rst==1) state_reg <= start;

else state_reg <= next_state;

end

//Output Logic

assign dout_bit = (((state_reg == rd0_twice) && (din_bit == 0) || (state_reg == rd1_twice) && (din_bit ==1))) ? 1 : 0;

endmodule

📄 Test Bench 코드

module tb_seq_det_mealy;

// Inputs

reg clk;

reg rst;

reg din_bit;

// Outputs

wire dout_bit;

wire [2:0] state_reg, next_state;

// Instantiate the Unit Under Test (UUT)

seq_det_mealy uut (

.clk(clk),

.rst(rst),

.din_bit(din_bit),

.dout_bit(dout_bit),

.state_reg(state_reg),

.next_state(next_state)

);

always #5 clk = ~clk;

initial begin

clk = 0;

rst = 1;

din_bit = 0;

#10 rst = 0;

// Test 1: Single 0, Single 1

#10 din_bit = 0; // Start with 0

#10 din_bit = 1; // Change to 1

// Test 2: Two consecutive 0s

#10 din_bit = 0;

#10 din_bit = 0;

// Test 3: Two consecutive 1s

#10 din_bit = 1;

#10 din_bit = 1;

// Test 4: Mixed sequence (0 -> 1 -> 0 -> 0 -> 1 -> 1 -> 0)

#10 din_bit = 0;

#10 din_bit = 1;

#10 din_bit = 0;

#10 din_bit = 0;

#10 din_bit = 1;

#10 din_bit = 1;

#10 din_bit = 0;

// End simulation

#20 $stop;

end

endmodule

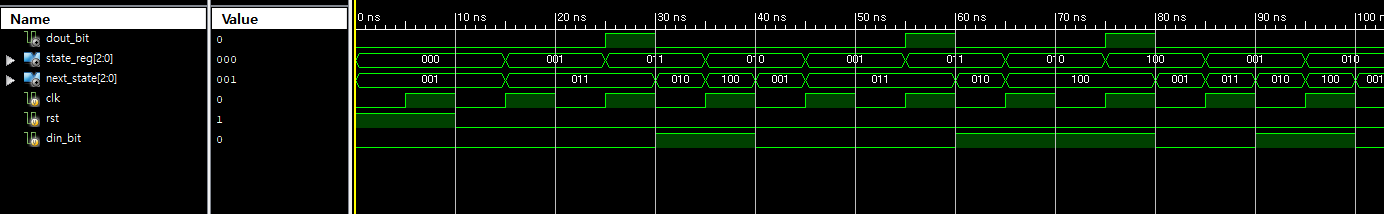

📄 출력 파형

✏️ 알게 된 것

dout_bit의 출력이 posedge clk이 들어오는 타이밍이 아닌데 바뀌는 것을 보고 의문이 들었는데, 그건 Mealy 머신의 구조적인 특성 때문이라고 한다.

*Mealy 상태 머신은 출력이 현재 상태와 입력에 의해 결정되기 때문에 입력 값이 바뀌면 클럭 신호와 상관없이 즉시 출력에 영향을 준다.

→ 설계한 회로를 보면 posedge clk 타이밍에 맞춰 변화하는 것은 state_reg(현재 상태) 값이고, next_state의 경우 입력 값이 바뀌는 순간 값이 변화하는 것을 알 수 있다.

'Electronic Engeneering > Hardware Description Language' 카테고리의 다른 글

| Verilog 자판기 설계 (code, tb, RTL 합성회로, 파형) (0) | 2024.12.12 |

|---|